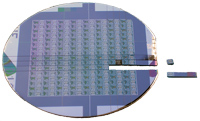

Wafer

Ce projet n'est pas tout à fait comme les autres, je n'ai pas le matériel pour faire cela à la maison mais c'est un projet que j'ai fait pendant mes études qui m'a vraiment beaucoup plu.

Ce wafer a été conçu lors d'un stage à l'AIME (Atelier Interuniversitaire de MicroElectronique) lorsque j'étais en 3ième année à l'ENSEIRB à Bordeaux. Cet "atelier" comporte une salle blanche qui permet de découvrir les différentes étapes de réalisation d'un circuit intégré. Mais pas en simple spectateur, en effectuant nous même toutes les opérations d'alignement, de gravure, nettoyage, séchage, recuit, etc. Le wafer est fait à partir d'un jeu de 4 masques destinés à la fabrication de circuits NMOS à enrichissement, à grille auto-alignée (process AIME AN4).

Le réticule contient 64 répétitions d’un bloc de 4 puces dites C1, C2, C3 et C4.

- C1 et C2 contiennent des dispositifs élémentaires destinés à la caractérisation électrique

- C3 et C4 contiennent des circuits intégrés basés sur la porte NOR

Après analyse des performances de chaque puce, une puce parmi celles qui sont fonctionnelles (une grain de poussière suffit à rendre une puce défectueuse) a été mise en boîtier TO (cliquez sur l'image ci contre pour voir le détail de la puce). Pour plus d'information sur la composition des puces et sur le jeu de masques utilisé, c'est ici.